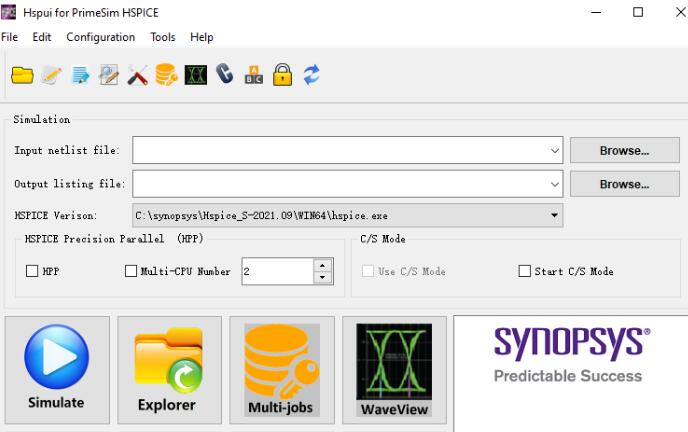

HSPICE激活版下载 Synopsys PrimeSim HSPICE S-2021.09 安装授权破解版(附破解文件+教程)

PrimeSim HSPICE是一款精确电路仿真器软件,它分享一流的仿真及分析算法,知识兔使用经代工厂认证过的 MOS 器件模型进行仿真。Synopsys很高兴地宣布PrimeSim HSPICE 2021.09 的可用性,该软件是业界用于精确电路仿真的“黄金标准”。

对于片上仿真, 模拟设计、RF 设计、定制数字设计、标准单元设计和特征化、存储器设计和特征化,知识兔以及器件模型开发。对于片外信号完整性仿真: 硅到封装到电路板到背板的分析和仿真以及完整的仿真环境,分享具有最新仿真和分析算法的经晶圆代工厂认证的MOS器件模型。HSPICE在模拟/ RF /混合信号IC设计,单元和存储器特性以及芯片/封装/电路板/背板信号完整性仿真中得到了广泛的应用,是业界最受欢迎,最受信任和最全面的电路仿真器。

功能特色

一、代工厂认证的模型

器件模型是进行精确电路仿真的要素。HSPICE始终是第一个分享新的高级设备模型的公司,并且知识兔HSPICE模型是第一个通过铸造厂认证的产品。多年来,HSPICE始终为先进的节点CMOS,FinFET和FDSOI工艺设计先进的建模技术,知识兔以确保分享最先进,最准确的一组行业标准器件模型实现。Synopsys与领先的商业和专有铸造厂紧密合作,知识兔以确保其HSPICE模型参数能够及时,准确地验证其制造过程。从最先进的技术节点上的紧凑建模委员会(CMC)标准化模型(BSIM,PSP,HiSIM等)到专有模型(HVMOS, TFT等),知识兔用于特殊应用(高压,显示器等)。参见www.HSPICE。

com,知识兔以获取HSPICE支持的设备型号的最新列表。

1、三重DES加密

HSPICE分享了符合三重数据加密标准(DES)的强大的192位加密。此功能使用户可以在不泄露敏感信息的情况下分发其HSPICE自定义网表和模型。加密的HSPICE网表的第三方收件人可以使用模拟运行,但不能打印加密的参数或内部节点电压。模拟加密网表的第三方用户将设备和电路视为黑匣子,仅分享终端功能。这使网表分享商可以保留其专有模型和设计保密,同时允许第三方执行晶体管精确的仿真而无需更改其流程

二、模拟/ RF /混合信号IC设计

1、运行时性能-单核和多核仿真

HSPICE的仿真精度,“开箱即用”的收敛性以及所有电路类型的运行时性能仍然是HSPICE研发团队的第一要务。Synopsys R&D不断发布,在不牺牲准确性的情况下提高了HSPICE的运行时性能。在过去的两年中,HSPICE在一个内核上的运行时性能在大型前后布局模拟,混合信号和内存设计上平均提高了5倍以上。此外,HSPICE交付了卓越的多核可扩展性,在16个核上的平均速度提高了8倍

2、与Synopsys Custom Compiler™和Custom WaveView™集成

Synopsys Custom Compiler为模拟,RF和混合信号设计人员分享了从前到后,知识兔从原理图到版图的现代设计驾驶舱,并全面支持HSPICE。请访问:www.Synopsys.com>芯片设计和验证>定制设计。

3、Verilog-A行为建模

Verilog-A已被证明是描述模拟电路行为和复杂的测试台输入刺激的理想语言。

使用HSPICE的符合LRM 2.4标准的编译Verilog-A模拟,用户可以在同一网表中混合晶体管级和Verilog-A行为描述,并提高运行时性能。

4、可靠性意识验证-过程可变性和MOSRA设备可靠性分析

复杂的分析(例如HSPICE MOSRA,最坏情况的拐角,蒙特卡洛,ACMatch和DCMatch)使用户能够优化电路,知识兔从而满足各种工艺,电压,温度范围和器件使用年限的设计约束。除了设备工艺变化之外,HSPICE和StarRC一起可以支持互连变化。HSPICE不仅报告了变化对产量的影响,而且知识兔确定了关键的产量限制设备和参数。用于良率特征的HSPICE设计包括:•极端情况分析:HSPICE可以轻松地探索设计的工艺角点和操作条件,知识兔以便分析其良率,功率和性能•Smart Monte Carlo采样:拉丁文超立方体采样和低差异序列可提高效率准确的产量分析•Sigma Amplification:通过比例因子增加SPICE模型中的工艺变化,知识兔从而以更少的样品和更快的周转时间覆盖高σ变化分析。大型混合信号IP鲁棒性验证的理想选择•ACMatch和DCMatch:用于分析因局部变化而引起的参数失配效应•变化块:用于定义过程变化效应的强大而灵活的机制•MOSRA设备可靠性分析:模拟HCI和NBTI设备的老化效应

5、回路稳定性分析

HSPICE的环路稳定性分析使用户能够在频域中分析反馈电路上的环路增益和相位特性。

6、瞬态噪声分析

HSPICE的瞬态噪声分析使用户能够预测设备噪声(通道,热,闪烁和散粒噪声)对时域波形的影响。瞬态噪声分析可用于表征PLL应用的相位噪声和抖动。

多样本蒙特卡洛样本生成一组噪声刺激波形,知识兔以进行统计评估。HSPICE支持噪声带宽和缩放控件,并使用户能够绘制仿真结果的直方图。

7、大信号周期稳态分析

HSPICE可以执行主要的大信号分析,知识兔包括周期性稳态(PSS)分析,周期性噪声和相位噪声分析以及周期性AC分析,知识兔以及使用Shooting Newton(SN)引擎(用于强非线性电路)或谐波平衡(HB)引擎(用于弱非线性电路)。HSPICE可以快速而准确地模拟大型非线性高频设计。知识兔借助一整套专业分析,HSPICE是传统

三、单元和内存表征

HSPICE是执行精确的单元和存储器表征的理想选择,并基于仿真数据分享了多种波形测量功能。数据驱动的参数扫描通过同时更改参数来自动表征,知识兔以方便地处理数百个HSPICE仿真参数。

1、性能提升

HSPICE显着提高了其性能(读取,仿真和总吞吐量),同时保持了相同的高精度。改进的仿真性能是通过增强的时间步控制算法以及简化的仿真控制界面实现的。用户可以使用单个控制选项同时缩放模拟选项,而无需用户调整多个选项设置。HSPICE自动调整每个时间步长和其他仿真选项,知识兔以达到所需的精度水平。

2、改善整合

HSPICE的客户端服务器模式选项使用户可以加快仿真速度和总周转时间。当运行带有客户端服务器模式选项的HSPICE时,HSPICE通过最大程度地减少对模型和网表的重新读取以及最小化许可证签入和签出的次数来缩短总的周转时间。通过改进的性能以及与单元和存储器特性描述环境的集成,HSPICE可以快速轻松地探索大型单元和存储器库中的多个过程角落和操作条件。

四、芯片/封装/板/背板信号完整性(SI)仿真

1、高级元素和来源

随着芯片和电路板速度的不断提高,新的设计和验证挑战不断涌现。HSPICE揭示了由抖动,串扰,振铃,接地反弹和其他噪声源引起的信号完整性问题。凭借广泛的模型和元素支持,HSPICE是唯一可以满足您的芯片到封装,板到板到背板SI仿真需求的仿真器。

2、S元素

用户可以根据网络分析仪的直接测量值或现场求解器的解决方案轻松创建准确的S参数模型。HSPICE支持具有任意数量的差分和单端端口的S参数模型。HSPICE的递归卷积算法可以快速准确地模拟具有1000个端口的S参数,知识兔适用于大型包装和其他应用。HSPICE直接使用.LIN命令分享S参数提取,知识兔从而实现更准确,详细的测量。

3、钨元素

通过处理介电损耗,HSPICE的W元件可以准确模拟50英寸,50 GHz传输线。另外,知识兔可以将S参数合并到W元素中以进行互连仿真。

4、更多来源,元素和模型

HSPICE支持伪随机和位模式源,E&G元素,IBIS模型以及更多满足您所有SI模拟需求的功能。

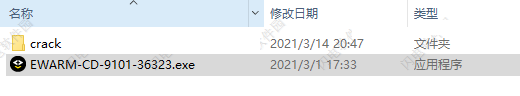

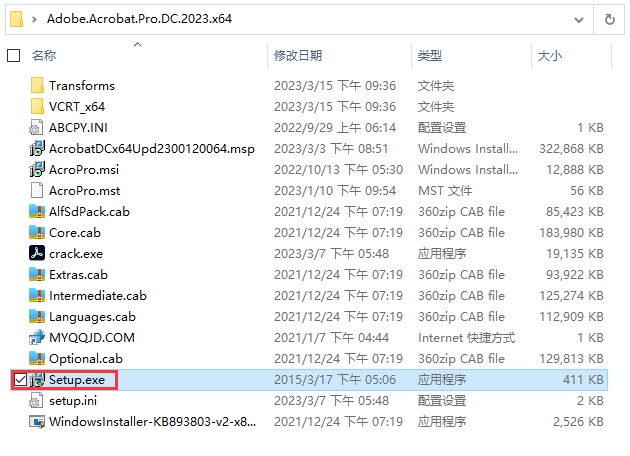

安装教程

1、在知识兔下载并解压,首先,确保您的计算机仅通过网卡(最好是以太网)连接到Internet,并且知识兔已禁用防病毒功能。然后知识兔运行hspice_vS-2021.09_win.exe进行安装

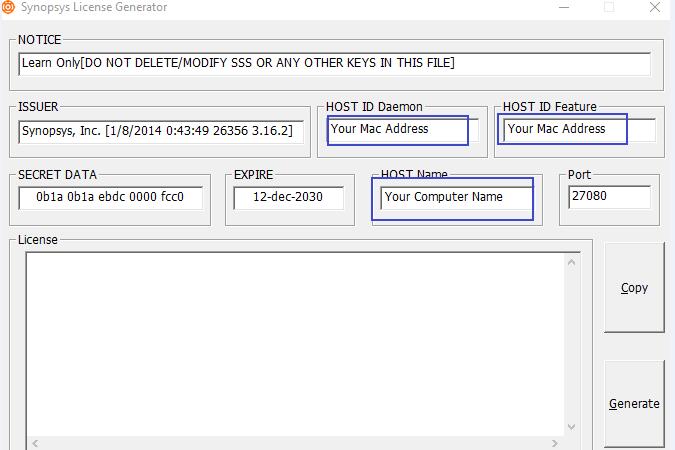

2、运行“scl_keygen.exe”,单击“generate”,等待文本显示在“license”部分中。并运行“lic_patch.bat”以修复它

3、知识兔将“synopsys_lic.dat”复制到您想要的位置。

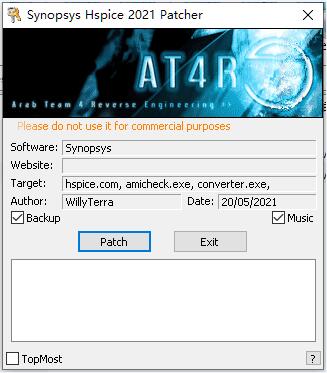

4、知识兔将“Synopsys HSpice 2021 Patcher.exe”复制到Synopsys软件根目录(例如:C:\Synopsys\)并运行它,单击补丁按钮并等待。

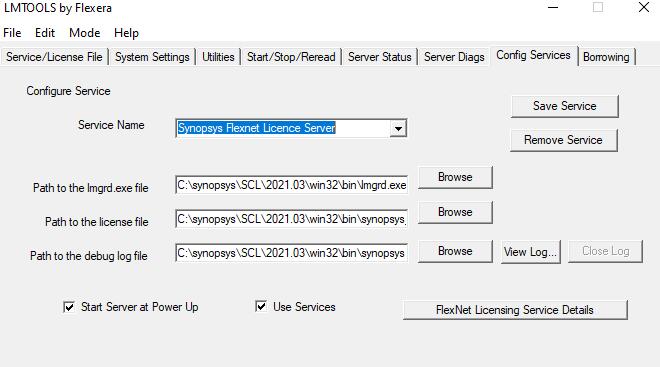

5、打开lmtools设置synopsys许可证服务器并启动它。

6、设置用户环境变量:

名称:SNPSLMD_LICENSE_FILE

值:许可证文件

在lmgrd的路径部分中,单击浏览选项,然后知识兔选择lmgrd.exe文件。在许可证文件的路径部分中,单击浏览选项,转到C:\ synopsys \ SCL \ 2021.09,在窗口的右下角单击“许可证文件(* .Lic)”,然后知识兔单击许可证文件(* .Dat),然后知识兔选择并打开出现的Synopsys.dat文件。在“调试日志文件的路径”部分中,替换为C:\synopsys\SCL\2021.09\debug.log

下载仅供下载体验和测试学习,不得商用和正当使用。