quartus21破解版下载 FPGA设计软件Intel Quartus Prime Pro Edition v21.4 破解版(附激活补丁)

Quartus Prime专业破解版是一款FPGA设计软件,包含设计英特尔FPGA、SoC和CPLD所需的一切。这包括设计输入、综合到优化、验证和仿真。Quartus显着提高了具有数百万个逻辑元件的设备的功能,为设计人员分享了下一代设计机会的理想平台。软件经过优化以支持Intel下一代FPGA和SoC中的高级特性,知识兔从Arria 10器件系列开始。当开始新的Arria 10设计或Arria 10设计需要仅在Quartus Prime Pro Edition软件中可用的功能时,知识兔使用Quartus Prime Pro Edition软件。欢迎需要此款工具的朋友前来下载体验。

英特尔 Quartus Prime 专业版概述

该软件为最先进的英特尔 Agilex、英特尔 Stratix 10、英特尔 Arria 10 和英特尔 Cyclone 10 GX FPGA 和 SoC 设计分享了一个完整的设计环境。

其 GUI 支持轻松的设计输入、快速的设计处理、直接的设备编程以及与其他行业标准 EDA 工具的集成。用户界面使您可以轻松地专注于您的设计,而不是设计工具。模块化编译器简化了 FPGA 开发过程,并确保以最少的工作获得最高的性能。

它分享灵活的设计方法、高级综合并支持最新的英特尔 FPGA 架构和分层设计流程。Compiler 分享强大且可定制的设计处理,知识兔以实现硅的最佳设计实现。

英特尔 Quartus Prime 专业版的特点

Qsys:下一代系统集成工具。该工具在 FPGA 设计过程中节省了大量时间和精力。

Powerplay Power Analyzer:从初始设计的概念到计划的执行来估计消耗的能力

System Console:系统级调试工具,可帮助您快速实时调试 FPGA 设计。

合成:一种新的合成引擎,将新的语言解析器集成到软件中。使用此解析器,设计人员可以看到改进的 RTL 语言。

用于识别校准问题和测量每个 DQS 信号的裕量的外部存储器接口工具。

DSP Builder:MATLAB / Simulink 和 Quartus II 软件之间无缝集成的工具

SoCEDS:一套开发工具,知识兔用于开发 SoC FPGA 软件的有价值的应用程序

高速顺序债券的绩效评估

技术细节和系统要求

支持的操作系统:Windows 11 / Windows 10 / Windows 8.1 / Windows 7

处理器:多核 Intel 系列或更高版本,Xeon 或 AMD 同等产品

内存:4GB(推荐 8GB 或更多)

可用硬盘空间:推荐 10GB 或更多

Quartus Prime21安装激活教程

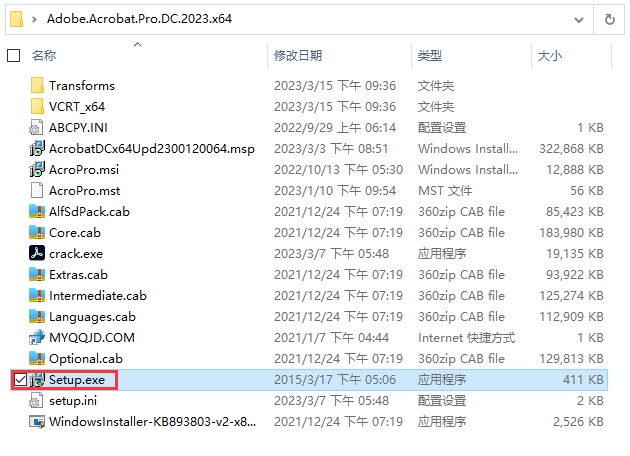

1、知识兔下载并解压,如图所示

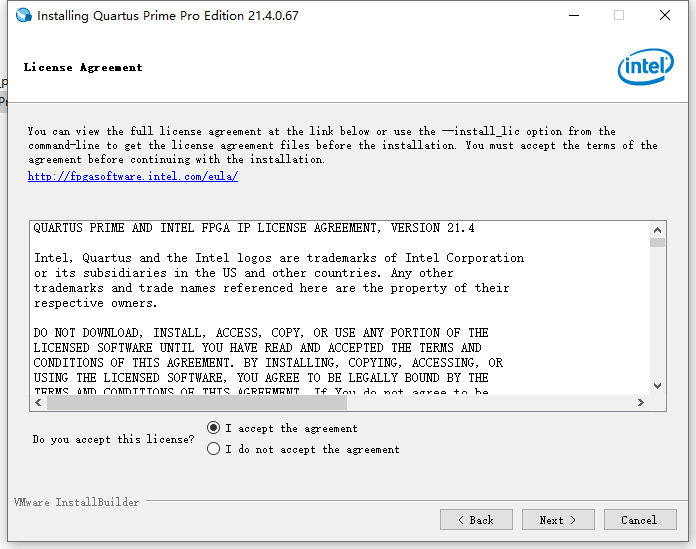

2、安装程序,勾选我接受协议

3、安装位置

4、安装完成,在文本编辑器中打开 Lic_Q21+IP.dat 并将“XXXXXXXXXXXX”替换为您的 MAC 地址

您可以通过打开 cmd.exe 并运行“ipconfig /all”来找到 MAC 地址

5、知识兔将Lic_Q21+IP.dat复制到’C:\intelFPGA_pro\21.4\’

6、知识兔将 sys_cpt.dll 复制到 ‘C:\intelFPGA_pro\21.4\quartus\bin64’,替换现有文件。

7、知识兔将环境变量 ALTERAD_LICENSE_FILE 设置为“C:\intelFPGA\21.4\Lic_Q21+IP.dat”。

8、享受!!

功能特色

1、编译策略

Intel Quartus Prime Pro Edition软件中的编译器是一种快速、多方面的工具,允许不同的编译策略来满足设计人员的需求。除了可以为您分享性能基准的标准编译之外,还有其他可用的编译选项:

新-小型设计的快速编译可用于在开发过程开始时进行快速编译,此时仅实现了一小部分设计。

新-快速功能测试编译用于快速检查RTL的功能性能。在没有设置优化的情况下执行保持时序优化。用于对Fmax不重要的硬件进行功能验证。

改进-积极的编译时间分享了快速功能测试编译和默认编译选项之间的中间地带。编译速度更快,仅适度降低Fmax。

高效率编译用于使编译器尽最大努力从设计中获得最佳性能结果。

改进-工程变更单(ECO)编译用于仅需要对其他良好编译进行微小更改时。ECO compiles可以分享5X–10X.2的编译加速。它取代了Rapid Recompile流程,知识兔用于适配后Signal Tap更改,显着提高编译速度。

此外,还有许多其他参数可用于自定义编译策略以满足您的特定要求。

2、Nios®V

Nios V是面向英特尔®FPGA的下一代软核处理器,基于RISC-V指令集架构。它为基于RISC-V的处理器利用了快速增长的开源生态系统。

第一个变体是Nios V/m

基于RISC-V:RV32IA分类

32位ISA

5级流水线

AXI4接口

英特尔硬件抽象层(HAL)和uC/OS-II支持

超过Nios®II/e内核5倍的性能

3、新报告

英特尔®Quartus®Prime专业版软件继续扩展其丰富的编译报告集。在v21.3软件版本中,新增了以下报告:

报告时钟网络

报告异常可达性(测试版)

按源文件报告时间

并且知识兔重新组织了静态时序分析报告任务,知识兔以便更轻松地处理最常用的任务。

除了新的和改进的报告之外,其中许多还支持报告之间的交叉探测。这种不断扩展的报告组合使您能够收集有关路由、拥塞、时序、张力、跨度、路由工作量和许多其他指标的详细信息,这些指标将为快速关闭时序分享快速反馈。

4、调试工具

保留调试信号:

在Quartus RTL流程和Platform Designer中保留用于调试的信号允许设计人员在整个编译过程中保持节点的可见性。当使用Quartus Debug Tools时,标记的节点会显示在Node Finder GUI中。标记要保留以供调试的信号可以在逐个信号的基础上、在实例/实体级别完成,或者通过编译指示(Verilog)或属性(VHDL)为整个设计打开和关闭。

分享的报告将显示所有已保存的信号以及所需设置已成功应用。

带有ECO编译器的增量信号抽头:

许多新功能已添加到用于增量Signal Tap编译的ECO编译器中。

将适配后抽头输入更改为基本OR触发器

更改高级触发器(适配后输入和/或逻辑)

增加适配后知识兔点击目标的数量

将合成前抽头转换为拟合后抽头

此外,还对Signal Tap GUI进行了改进,使这些功能使用起来更加直观。在设计验证的最后阶段使用Signal Tap时,ECO编译器显着缩短了重新编译时间。

模拟器感知信号抽头(测试版):

英特尔®Quartus®Prime Pro软件版的21.3版分享了一项激动人心的新创新,即添加了模拟器感知Signal Tap节点。设计人员可以使用RTL仿真器的全部功能来扩展从FPGA设计中获取的Signal Tap数据的范围。

用户不是选择单个节点,而是选择他们想要调试的层次结构或实例。新的智能节点查找器将识别分享实例完整可见性所需的时钟域和节点。捕获Signal Tap数据后,用户将该数据导出到他们首选的RTL模拟器中。Quartus将生成仿真脚本并导出捕获的数据以加载到仿真器中作为仿真的起点。从那里,用户可以使用Signal Tap数据作为仿真的初始条件,全面了解他们的设计。这使用户不必经历如此多的添加或更改Signal Tap节点和重新编译的迭代,知识兔从而节省了设计人员在调试和验证阶段的大量时间。

5、远程调试

远程调试解决方案已扩展为使用ARM HPS通过以太网或PCIe进行通信。

6、平铺界面规划器

英特尔®Quartus®Prime Tile Interface Planner是一项新功能,可帮助您将组件IP快速放置在F-tile的合法tile位置。Tile Interface Planner是一种交互式布局规划工具,可简化组件IP在设备块上的合法放置。

Tile Interface Planner在分层树视图中显示您的项目组件IP,旁边是设备tile段的可视表示。然后知识兔,您可以在tile中找到每个IP的潜在合法位置,将IP放置在该位置,并将放置约束应用于下游编译器阶段的项目。

下载仅供下载体验和测试学习,不得商用和正当使用。